# ENHANCED GAUSSIAN BACKGROUND MODELING ALGORITHM AND IMPLEMENTATION IN FPGA FOR REAL-TIME MOVING OBJECT DETECTION IN SURVEILLANCE VIDEO

**GE GUO**

September 2014

# ENHANCED GAUSSIAN BACKGROUND MODELING ALGORITHM AND IMPLEMENTATION IN FPGA FOR REAL-TIME MOVING OBJECT DETECTION IN SURVEILLANCE VIDEO

Ge Guo

Department of Geodesy and Geomatics Engineering

University of New Brunswick

P.O. Box 4400

Fredericton, N.B.

Canada

E3B 5A3

September 2014

© Ge Guo, 2014

### **PREFACE**

This technical report is a reproduction of a thesis submitted in partial fulfillment of the requirements for the degree of Master of Science in Engineering in the Department of Geodesy and Geomatics Engineering, September 2014. The research was supervised by Dr. Yun Zhang (Department of Geodesy and Geomatics Engineering) and Professor Mary E. Kaye (Department of Electrical and Computer Engineering), and funding was provided by the Canada Research Chair (CRC) Program and the Atlantic Innovation Fund (AIF). The software and lab equipment used in this research was provided by Canadian Microelectronics Corporation Microsystems.

As with any copyrighted material, permission to reprint or quote extensively from this report must be received from the author. The citation to this work should appear as follows:

Guo, Ge (2014). Enhanced Gaussian Background Modeling Algorithm and Implementation in FPGA for Real-Time Moving Object Detection in Surveillance Video. M.Sc.E. thesis, Department of Geodesy and Geomatics Engineering, Technical Report No. 295, University of New Brunswick, Fredericton, New Brunswick, Canada, 108 pp.

### **ABSTRACT**

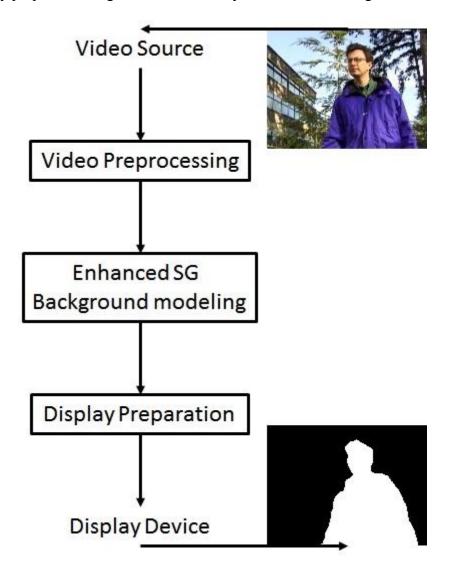

A real-time solution of moving object detection (MOD) in surveillance video was explored in this work motivated by the practical need of real-time automated video analysis system. The core element of a moving object detection process is its background modeling algorithm in the content of surveillance and road monitoring applications. By reviewing and analyzing previous works, single Gaussian (SG) background modeling algorithm was selected and enhanced. Then a circuit that performs MOD with enhanced SG algorithm was designed and implemented in a Virtex6 FPGA of a ML605 evaluation board with other hardware components. The experiment results showed that the proposed MOD system could perform real-time MOD in a video of 1280×720p@30fps. It outperforms the software experiments/implementations and the state-of-art FPGA-based implementations.

# **DEDICATION**

To my most supportive parents, Yawei Guo and Suyi Lv.

To my most beloved one, Sixian Zhang.

## **ACKNOWLEDGEMENTS**

I would like to express my respect and sincere gratitude to my supervisors Professor Yun Zhang and Professor Mary Kaye for their helpful suggestions and guidance during the whole course of this work.

# **Table of Contents**

| ABS  | STRACT   |                                                               | ii    |

|------|----------|---------------------------------------------------------------|-------|

| DEI  | DICATIO  | ON                                                            | iii   |

| AC]  | KNOWL    | EDGEMENTS                                                     | iv    |

| Tab  | le of Co | ntents                                                        | v     |

| List | of Table | es                                                            | viii  |

| List | of Figur | res                                                           | ix    |

| I.   | Introdu  | ection                                                        | 1     |

| 1    | .1. Ba   | ckground and Motivation                                       | 1     |

| 1    | .2. Re   | eal-Time Definition                                           | 7     |

| 1    | .3. Pr   | oblem Statement                                               | 8     |

| 1    | .4. Pr   | oblem Breakdown and Thesis Organization                       | 8     |

| II.  | Literat  | ure Review                                                    | 10    |

| 2    | .1. Re   | eview of the Alternative Hardware Platforms                   | 10    |

|      | 2.1.1.   | DSP Platform Review                                           | 10    |

|      | 2.1.2.   | FPGA Platform Review                                          | 14    |

|      | 2.1.3.   | Summary                                                       | 18    |

| 2    | .2. Re   | eview of Milestone Statistical Background Modeling Algorithms | 19    |

|      | 2.2.1.   | Common Ground of Statistical Background Modeling Algorithm    | ns 19 |

|      | 2.2.2.   | Single Gaussian Algorithm                                     | 20    |

|      | 2.2.3.   | Mixture of Gaussian Algorithm                                 | 22    |

|      | 2.2.4.   | Kernel Density Estimation (KDE)                               | 24    |

| III. | Solutio  | n Develonment                                                 | 27    |

| 3.1. A      | gorithm Selection and Improvement                  | 27 |

|-------------|----------------------------------------------------|----|

| 3.1.1.      | Memory Related Considerations                      | 27 |

| 3.1.2.      | Algorithms Analysis and Comparison                 | 30 |

| 3.1.3.      | SG Algorithm Enhancement                           | 30 |

| 3.2. Pr     | e-knowledge and System Features                    | 51 |

| 3.2.1.      | Pre-mentioned Facts                                | 51 |

| 3.2.2.      | Transferring Video Data in Real-Time               | 52 |

| 3.2.3.      | Pipelining Structure                               | 53 |

| 3.2.4.      | System Feature Extraction                          | 54 |

| 3.3. Pr     | oposed Design                                      | 55 |

| 3.3.1.      | System Level Descriptions                          | 55 |

| 3.3.2.      | Functional Blocks Descriptions                     | 59 |

| IV. Impl    | ementation and Evaluation                          | 68 |

| 4.1. Re     | eal-Time MOD Design Implementation                 | 68 |

| 4.1.1.      | Circuit Implementation with EDA tools              | 68 |

| 4.1.2.      | Hardware Connection                                | 69 |

| 4.2. Ex     | xperiment Result                                   | 70 |

| 4.2.1.      | Real-Time Performance                              | 70 |

| 4.2.2.      | Detection Quality                                  | 71 |

| 4.3. Co     | omparison with Other Works                         | 72 |

| 4.3.1.      | Comparison with other Software Implementation Work | 72 |

| 4.3.2.      | Comparison with other FPGA Implementation Work     | 73 |

| V. Conclu   | ision and Future Work                              | 76 |

| 5.1. Ac     | chievements                                        | 76 |

| 5.2. In     | provements                                         | 76 |

| 5.3. Fu     | iture Work                                         | 77 |

| Bibliograph | y                                                  | 79 |

| Appendix I – Implementation Note        | 85  |

|-----------------------------------------|-----|

| FPGA Resource Utilization               | 85  |

| Design Files and Schematics Description | 85  |

| Glossary                                | 107 |

| Curriculum Vitae                        |     |

# **List of Tables**

| Table 1 Three-Level Image/Video Operations Characteristics                      | 5  |

|---------------------------------------------------------------------------------|----|

| Table 2 Parameters and Their Average Bits on Data Bus                           | 30 |

| Table 3 Optimized SG Constants and Maximum JC Coefficients of Each Data Set     | 37 |

| Table 4 Optimized Enhanced SG Constants and Maximum JC Coefficients             | 46 |

| Table 5 Comparison of Parameter Optimization between SG and Enhanced SG         | 47 |

| Table 6 Video Preprocessing Logic Blocks                                        | 60 |

| Table 7 IP Cores' Classification in the Design                                  | 69 |

| Table 8 Indirect Efficiency Comparison between Software and FPGA Implementation | 73 |

| Table 9 Real-Time Performance Comparison with Other FPGA Imlementations         | 74 |

| Table 10 FPGA Resource Utilization of the Design                                | 85 |

# **List of Figures**

| Figure 1 Three Steps in Automated Video Analysis                                      | 2          |

|---------------------------------------------------------------------------------------|------------|

| Figure 2 - Data Transformation within Automated Video Analysis System & Input / O     | utput Data |

| Relationship of 3 Levels of Image/Video Operations                                    | 4          |

| Figure 3 Typical Digital Signal Processing System Diagram                             | 11         |

| Figure 4 Memory Interface at PHY                                                      | 28         |

| Figure 5 MPMC Interface Diagram                                                       | 29         |

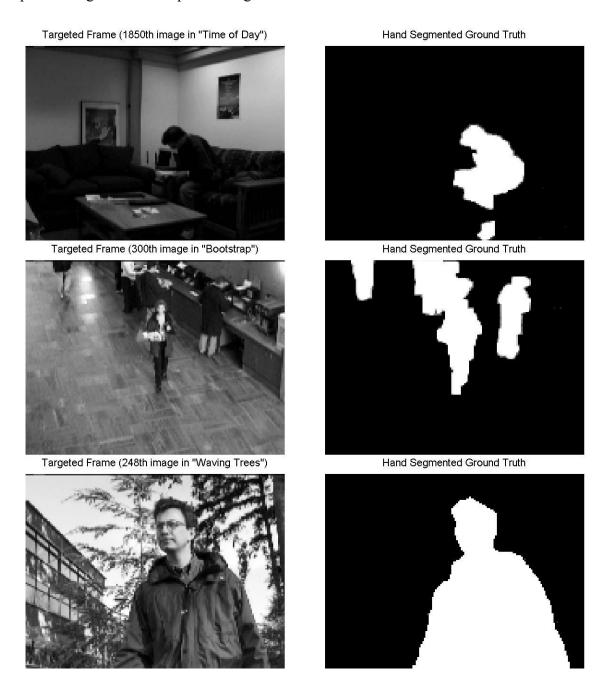

| Figure 6 – Targeted Frames and Their Ground Truth                                     | 33         |

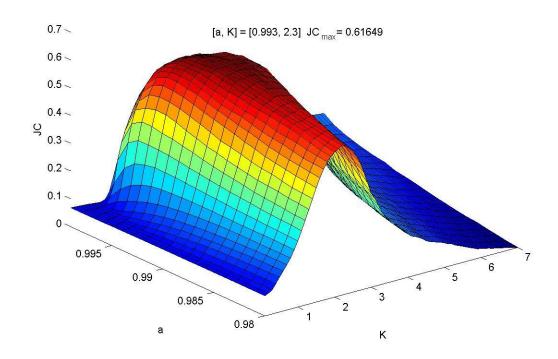

| Figure 7 K-a-JC Surface of 'Time of Day' Data Set                                     | 35         |

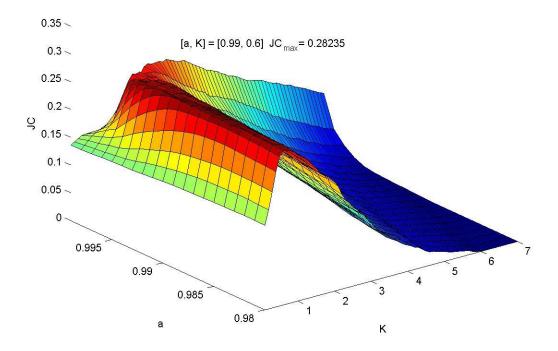

| Figure 8 K-a-JC Surface of 'Bootstrap' Data Set                                       | 36         |

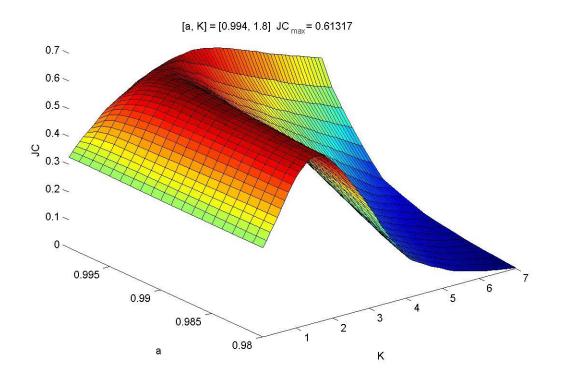

| Figure 9 K-a-JC Surface of 'Waving Trees' Data Set                                    | 37         |

| Figure 10 Targeted Frame, Ground Truth, and SG Segmented Result in 'Time of Day'      | 38         |

| Figure 11 Targeted Frame, Ground Truth, and SG Segmented Result in 'Bootstrap'        | 38         |

| Figure 12 Targeted Frame, Ground Truth, and SG Segmented Result in 'Waving Trees'     | 38         |

| Figure 13 Pixel Intensity, Mean, and Classification Boundaries at [118, 147]          | 39         |

| Figure 14 Pixel Intensity, Mean, and Classification Boundaries at [98, 14]            | 41         |

| Figure 15 Pixel Intensity, Mean, and Classification Boundaries at [35, 1]             | 42         |

| Figure 16 – Details of Start-up Period of Figure 15                                   | 42         |

| Figure 17 Th-JC curve of 'Time of Day' Data Set                                       | 45         |

| Figure 18 Th-JC curve of 'Bootstrap' Data Set                                         | 45         |

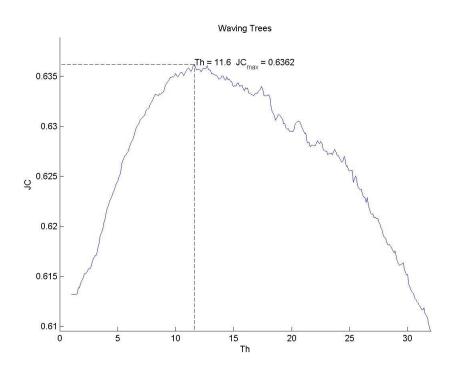

| Figure 19 Th-JC curve of 'Waving Trees' Data Set                                      | 46         |

| Figure 20 Pixel Intensity, Mean, and Enhanced Classification Boundaries at [118, 147] | 48         |

| Figure 21 Pixel Intensity, Mean, and Enhanced Classification Boundaries at [98, 14]   | 48         |

| Figure 22 Pixel Intensity, Mean, and Enhanced Classification Boundaries at [35, 1]    | 49         |

| Figure 23 – Details of Start-up Period of Figure 22                                   | 49         |

| Figure 24 Truth Ground, Original, and Enhanced Segmentation of 'Time of Day' Data set | 50         |

| Figure 25 Truth Ground, Original, and Enhanced Segmentation of 'Bootstrap' Data set    | 50 |

|----------------------------------------------------------------------------------------|----|

| Figure 26 Truth Ground, Original, and Enhanced Segmentation of 'Waving Trees' Data set | 51 |

| Figure 27 Transferring Data of a Frame (3-by-3)                                        | 52 |

| Figure 28 Virtual Timing Diagram of Transferring Video Data                            | 52 |

| Figure 29 Displaying a Frame from Data Stream                                          | 53 |

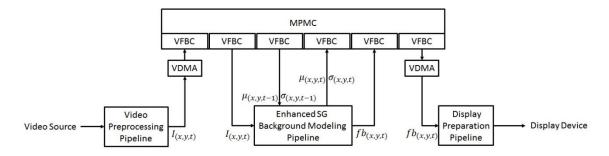

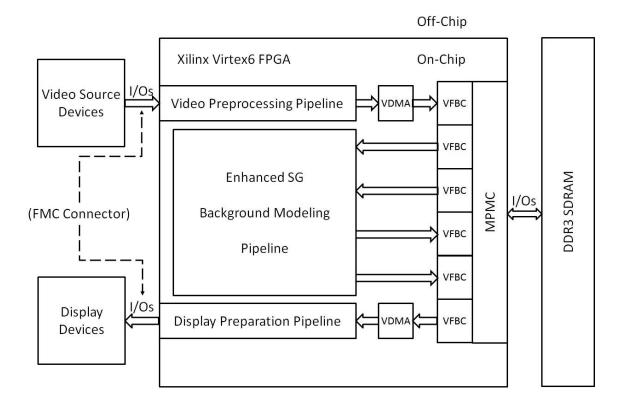

| Figure 30 System Work Flow Diagram                                                     | 56 |

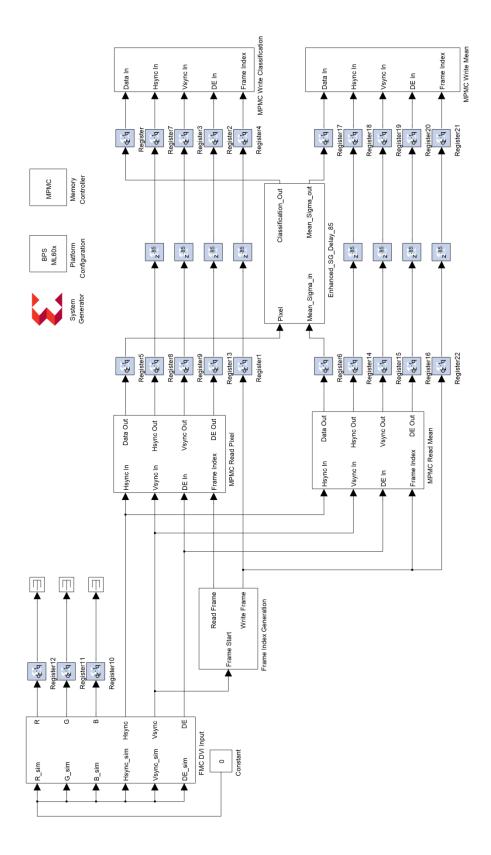

| Figure 31 System Data Flow Diagram                                                     | 57 |

| Figure 32 System Structure Diagram.                                                    | 58 |

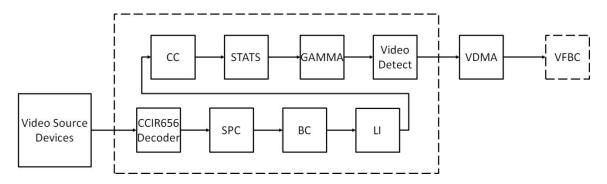

| Figure 33 Video Preprocessing Pipeline Diagram                                         | 59 |

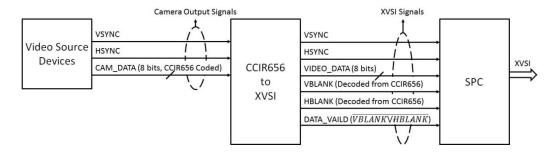

| Figure 34 First Major Format Change in Video Preprocessing Pipeline                    | 60 |

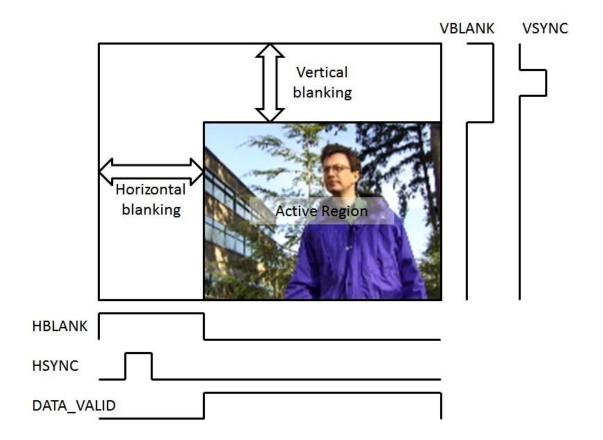

| Figure 35 XVSI Signals' Timing Diagram                                                 | 62 |

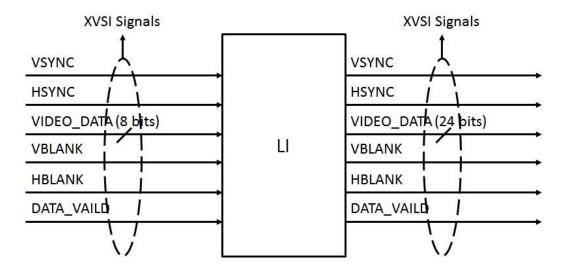

| Figure 36 Second Major Format Change in Video Preprocessing Pipeline                   | 63 |

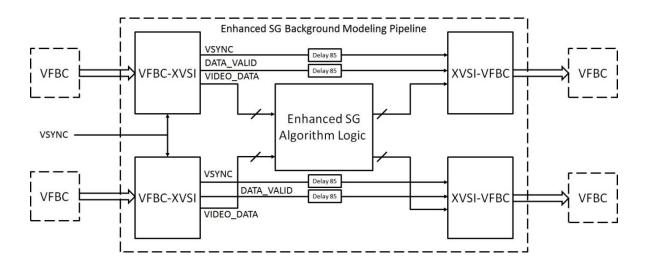

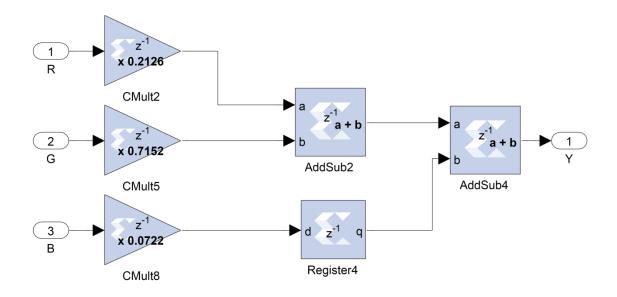

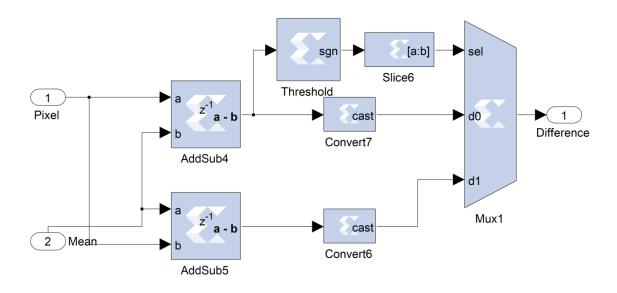

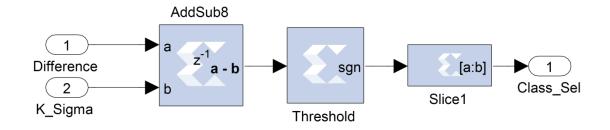

| Figure 37 Enhanced SG Background Modeling Pipeline                                     | 64 |

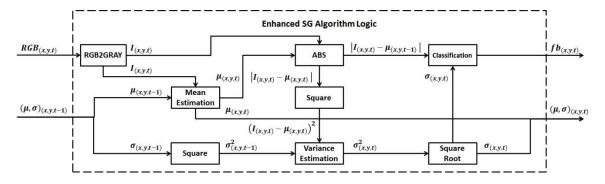

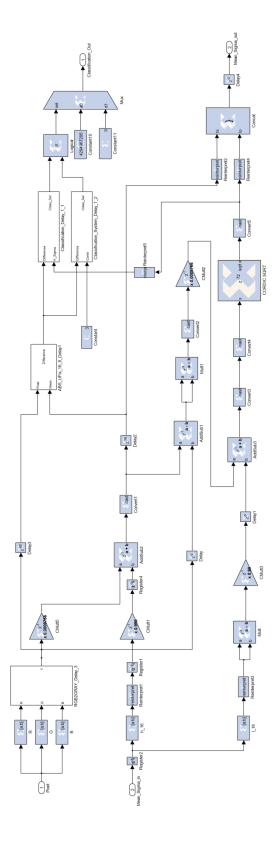

| Figure 38 Enhanced SG Algorithm Logic                                                  | 64 |

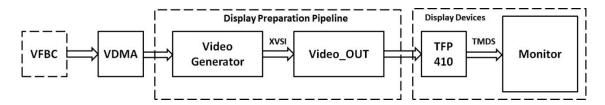

| Figure 39 Display Preparation Pipeline                                                 | 66 |

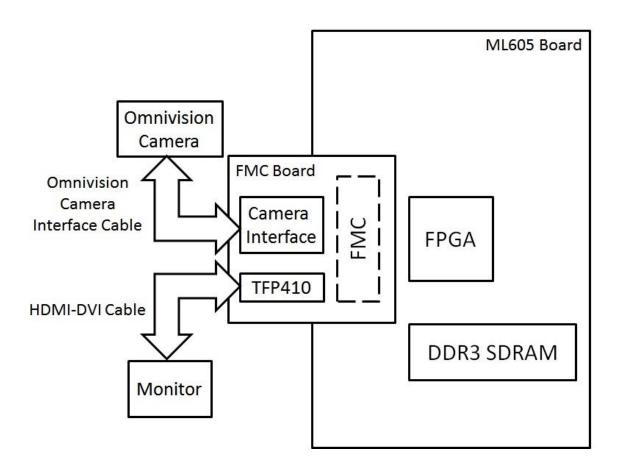

| Figure 40 Hardware Connection Diagram                                                  | 70 |

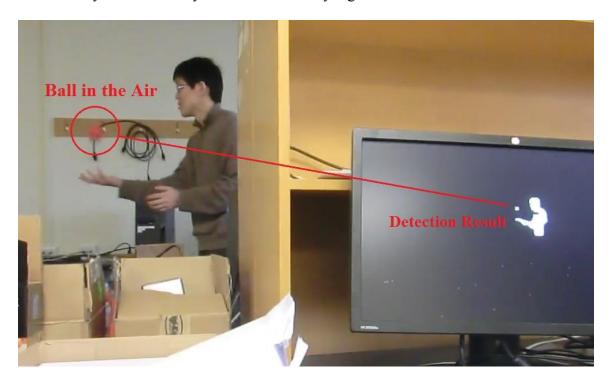

| Figure 41 Field Test: Detection of a Moving Ball                                       | 71 |

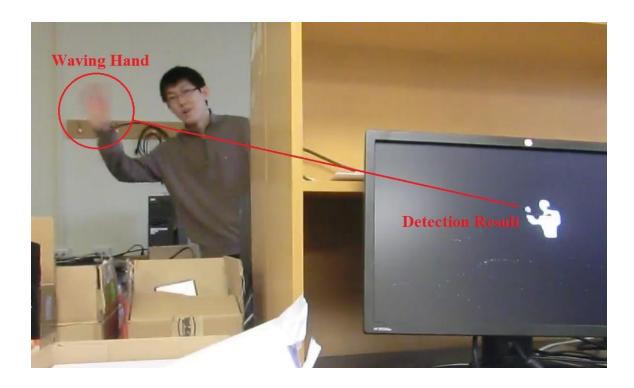

| Figure 42 Field Test: Detection of a Waving Hand                                       | 72 |

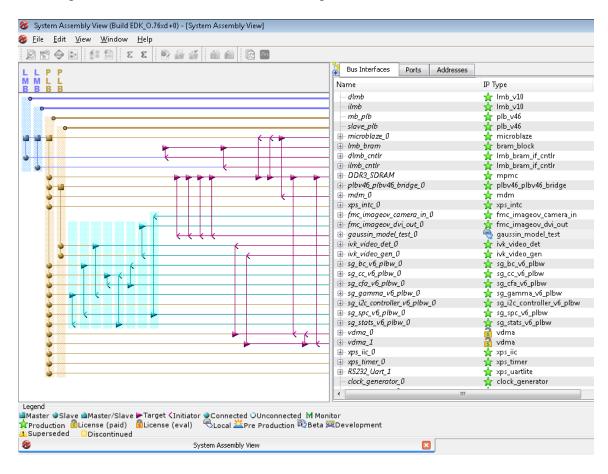

| Figure 43 Assembly View of the Design in XPS                                           | 87 |

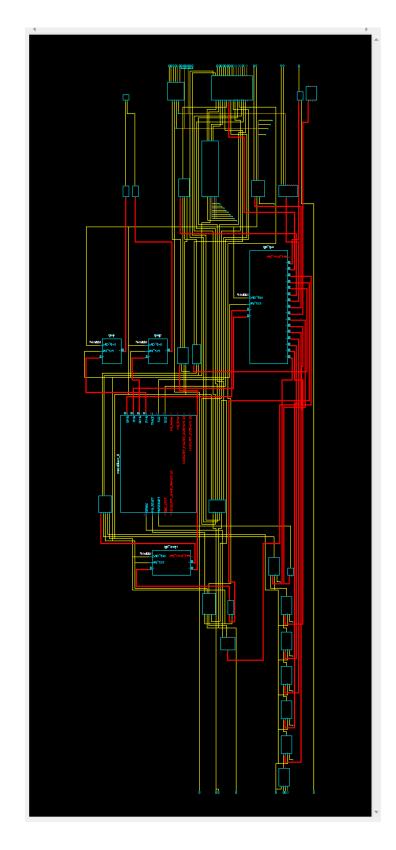

| Figure 44 Graphic View of the Design in XPS                                            | 88 |

| Figure 45 Enhanced SG Pipeline Top View in BPS                                         | 89 |

| Figure 46 – Enhanced SG Logic Block inside View in BPS                                 | 90 |

| Figure 47 RGB to Gray Logic Block inside View in BPS                                   | 91 |

| Figure 48 Absolute Operation Logic Block inside View in BPS                            | 91 |

| Figure 49 Classification Logic Block inside View in BPS                                | 92 |

### I. Introduction

### 1.1. Background and Motivation

Stationary cameras are often used in video surveillance and road monitoring systems. With the increasing concern of public safety, numerous stationary cameras are deployed across modern cities to cover as much area as possible. However, despite that so many cameras are deployed and they can run twenty-four-seven, the usage of the captured videos is rather primitive. According to a survey of 43 rail transit agencies in U.S., 2011 [1], the most common usage of surveillance video was 24-hours recording, and nearly one-half of the agencies did not monitor their cameras regularly, or at all, because of the personnel costs. A similar situation has also been a concern in UK, "With more than a million CCTV (Closed-Circuit Television) cameras in the UK alone, they are becoming increasingly difficult to manage," quoted from the New Scientist magazine [2]. "It is simple: we have so many cameras to capture video, but so few pairs of eyes." "If the technology takes off it could put an end to a longstanding problem that has dogged CCTV almost from the beginning." Indeed, if only there are extra pairs of "eyes" that can fill the vacancy caused by lack of man power to watch and analyze numerous video streams twenty-four-seven.

An automated video analysis system could be the extra pairs of "eyes". This kind of system can analyze the video stream(s) automatically without or with little people's attention and report only suspicious events to the professionals. With the assistance of automated video analysis system, the area covered by the surveillance cameras can be effectively monitored at last but only if the analysis is done in real-time. One benefit of analyzing video in real-time is the fast response to suspicious events. But there is another

reason for the system has to be real-time to be practical. That reason is there is no time to wait for post-processing in a twenty-four-seven working system. The detailed definition of real-time is introduced in section 1.2.

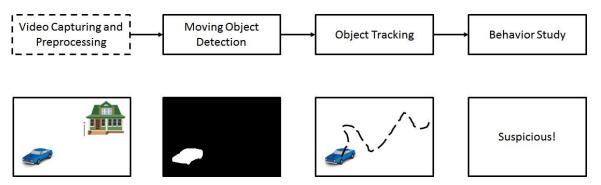

There are three key steps in an automated video analysis system identified by Yilmaz, Javed, and Shah [3]. Quoted from their work, these three steps are:

- 1) "Detection of interesting moving object."

- 2) "Tracking of such objects from frame to frame."

- 3) "Analysis of object tracks to recognize their behavior."

Figure 1 -- Three Steps in Automated Video Analysis

Figure 1 shows a simple example of an automated video analysis system. In this figure, three steps are connected together as a complete video processing chain.

In the first step, moving object detection (MOD) gives a bi-level image (image segmented into only two areas) from the current frame of video, where the region of moving object(s) (i.e., foreground) is labeled with 'white' and the region of other objects (i.e., background) is labeled with 'black'. Since this study is interested in moving object(s), the 'white' region is the 'region of interest' (ROI). Though the output is only bi-level, it remains a full size image, i.e., each pixel in the original video frame has a correspondent pixel in the segmented image.

In the second step, moving object tracking exploits information in the ROI and produces a trajectory of the moving car. This step usually involves three jobs in order. The first job is to tag the detected object(s) with image features (e.g., size, shape, texture, color, etc.) within the ROI of the original frame. The second job is to locate identified object(s) with the ROI's geometric properties. And the third job is to generate an up-to-date trajectory with up-to-date location information of the individual object. Note the trajectory is also a feature of the moving car.

In the third step, a "behavior study" deems the car's behavior "suspicious" and sends information accordingly. This step could be implemented with a pattern recognition system. A "suspicious event" could be defined as patterns of irregular trajectories. The output of the third step could be control signals triggering pre-defined actions. A predefined action here is sending information and could be anything like sending an alarm to authorities, recording the detected event, etc. In fact, this step can be implemented in various ways. However, in principle, the "behavior study" abstracts certain behavioral knowledge of the moving object(s) from the information provided by the previous step. And usually it also generates control signals according to the knowledge. Projection from knowledge to control signals is rather straight forward. If knowledge-to-control is taken as the last part of the system, the output of this step is control signals. Otherwise the output is behavioral knowledge of the moving object(s).

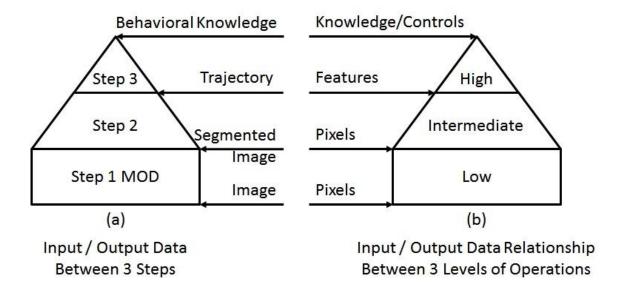

Input/output data between each step of the system is shown in Figure 2 (a).

Figure 2 – Data Transformation within Automated Video Analysis System & Input / Output

Data Relationship of 3 Levels of Image/Video Operations

Many research works can be found for each of the three steps that improve some algorithms in some way. But only a very small portion of the works takes real-time performance as the primary concern in modifying, designing, or implementing their algorithms. For the automated video analysis system to be practical, the author has taken improving the real-time performance as the primary focus in the thesis.

To determine which step will yield the most improvement, one needs to know the computational characteristics of the three steps and then a comparison is made. In getting the computational characteristics, one can either review tons of compatible previous works for each step or learn them from an established and well-defined model.

Figure 2 (b), illustrates the input/output data relationship between successive three levels of image/video operations. These three levels have been classified traditionally in image/video processing [4, 5, 6, 7], namely low level, intermediate level, and high level.

There is an obvious one-to-one correspondence between the three steps in Figure 2 (a) and the three levels in Figure 2 (b). One can learn the computational characteristics of each from this model if it is well defined.

By reviewing the works of [4, 5, 6, 7], the characteristics of the three levels' image/video operations are summarized as follows: The low level operations are usually regular, high-bandwidth demanding, and data-intensive, the high level operations are more irregular, low-bandwidth demanding, and control-intensive, and feature extraction operations are in-between at an intermediate level. Table 1 lists these characteristics. Compared to that of higher levels, *the low-level operations are usually considered as bottlenecks of efficiency within the image/video processing chain*, because they demand the most computational resources in terms of the quantity of computations and consumption of memory bandwidth [8] due to the amount of data to be processed. *Correspondingly, the first step, moving object detection (MOD) is the major concern in improving real-time performance.*

| Operation<br>Level | Operation<br>Structure | Memory Bandwidth<br>Consumption | Data/Control           |

|--------------------|------------------------|---------------------------------|------------------------|

| Low                | Regular                | High                            | Data Intensive         |

| Intermediate       | Regular                | Intermediate                    | Less Data<br>Intensive |

| High               | Irregular              | Low                             | Control Intensive      |

Table 1 -- Three-Level Image/Video Operations Characteristics

In terms of the moving object detection step, background subtraction is recognized as the most common approach for video captured by stationary cameras [3]. This is because the modern background subtraction approach is able to model the changes in the background [3]. The ability of modeling changes in background is due to state-of-art background modeling algorithms used in the background subtraction approach. Thus the performance of the moving object detection with a stationary camera highly depends on its background modeling performance if the background subtraction technique is applied. This point has been mentioned by other researches as well. Toyoma, et al. [9] pointed out that background subtraction is the 'common element' in surveillance systems with stationary cameras and also point out that the background modeling is the most difficult part in background subtraction. Cheung and Kamath [10], also clearly indicate that background subtraction is a common approach in moving object detection and the 'heart' of any background subtraction technique is the construction of a statistical model that describes the background. In summary, background modeling is the core element of moving object detection, if background subtraction is applied with a stationary camera, which is the most common setting for a video surveillance system.

With the focus on the background modeling within moving object detection, intensive research effort has been devoted to improving the robustness and adaptability of background modeling to date. Reviewing previous works [11, 12, 13] in the order of published date; the trend of increasing sophistication is evident in performing the statistical modeling for every pixel in a video. Modern cameras can provide video with resolution of several million pixels and can transfer several dozens of frames per second. With increasing sophistication in algorithms, real-time performance is not likely to be achieved on the conventional personal computers (PC) because most of CPUs are not created or specialized for massive data intensive workload [8]. And this issue has been reported by many other works. For example, Staffer and Grimson [12] implemented their proposed algorithm on an SGI O2 workstation and only get 11-13 frames per second (fps)

for a video of very low resolution at 160×120 pixels (p). Kristensen, Hedberg, and Jiang, et al. [14] also implemented the Staffer and Grimson's algorithm on a PC with an AMD4400+ processor and got only 4-16 fps for a video of 352×288p. Roshan and Zhang [15] examined the software implementation of several moving object detection algorithms and the experiment results also indicated that sophisticated background modeling algorithms are very time consuming running on conventional PC platform. Finding a feasible platform and implementing a suitable algorithm is the right way to improve real-time moving object detection.

### 1.2. Real-Time Definition

There are three common interpretations of 'real-time', namely 'real-time in the perceptual sense', 'real-time in the software programming sense', and 'real-time in the signal processing sense' [8]. Interpretation in the signal processing sense is used in this thesis, where 'real-time' means completing processing in the time available between successive input samples [16]. In the content of video processing, it means the algorithm must complete processing a frame between the start of a frame and start of the successive frame.

Note that the above definition does not give any specific number of how much time is available between two frames. It is because that time depends on the frame rate of the video. In other words, 'real-time in the signal processing sense' does not define exactly how fast the real-time performance is.

But how fast should it be to meet the desired frame rate? For an average multimedia display device, the screen needs to update at 30 fps (frame per second) for humans to

perceive continuous motion. Thus we consider executing the algorithm at 30 fps is the appropriate frame rate for real-time performance.

### 1.3. Problem Statement

In summary, the need of real-time automated video analysis motivates this research project. In investigating improvement of real-time performance, the MOD step becomes the major concern. Since a background modeling algorithm is the core element of the background subtraction approach that is most commonly used in MOD, the conventional implementation of background modeling algorithms is briefly reviewed. With increasing sophistication in background modeling algorithms, real-time performance is not likely to be achieved on conventional PCs because most of the CPUs used are not created or specialized for massive data intensive workloads.

Therefore, the aim of this thesis is to develop a real-time background modeling solution for moving object detection for a stationary camera using an alternative platform to the PC platform. The frame rate of the video captured by the camera should be no less than 30 fps. This goal is motivated by the need of automated video analysis in surveillance systems.

### 1.4. Problem Breakdown and Thesis Organization

Since the PC platform is infeasible for attempting real-time solution, the first issue was to decide on an alternative computing platform. The second issue was to select a suitable background modeling algorithm. Once the decisions were made, the next step was to devise a real-time moving object detection solution based on the selections. Then the solution was implemented and evaluated.

For solving the first issue, two types of hardware platforms were studied, namely DSP-based platforms and FPGA-based platforms. Each platform is introduced briefly and presented with implementation examples. For solving the second issue, several milestone background modeling algorithms are investigated, namely Single Gaussian Algorithm, Mixture of Gaussian Algorithm, and Kernel Density Estimation.

The decision of the platform was made based on the general performance of the presented examples. The decision of the algorithm involved some consideration of hardware features. Once the algorithm was selected, the algorithm was also improved to consider more hardware features in developing the real-time moving object detection solution. The design of the solution is presented by both high level and low level descriptions.

The proposed solution was implemented and evaluated. Evaluation includes experimental results and comparison with state-of-art works.

The contents of this these are organized in the chapters listed as following.

- Chapter 1: Introduction of this thesis including background, motivation, and problem statement.

- Chapter 2: Literature review of hardware platforms and background modeling algorithms.

- Chapter 3: Development of the real-time moving object detection solution.

- Chapter 4: Implementation and evaluation of the proposed solution.

- Chapter 5: Conclusion of the thesis and future works.

### **II.** Literature Review

This chapter reviews two subjects. The first subject is alternative hardware platforms.

The second subject is statistical background modeling algorithms.

The first review examines two types of platform, namely a DSP-based platform, and a FPGA-based platform. Both platforms considered can be used in embedded system.

The second review examines three algorithms, namely Single Gaussian Modeling (SG), Mixture of Gaussian Modeling (MOG), and Kernel Density Estimation Modeling (KDE).

### 2.1. Review of the Alternative Hardware Platforms

As discussed in section 1.1, the PC platform is not likely to support real-time background modeling algorithms, alternative hardware platforms are required. Considering that surveillance applications are likely to employ embedded systems, two types of hardware platforms that can be used to develop embedded systems are examined in this section. They are DSP-based platforms and FPGA-based platforms.

### 2.1.1. DSP Platform Review

### **DPS Introduction**

"DSP stands for Digital Signal Processor. It is a specialized microprocessor with an architecture optimized for the operational needs of digital signal processing.

Digital signal processing algorithms typically require a large number of mathematical operations to be performed quickly and repeatedly on a series of data samples. Signals (perhaps from audio or video sensors) are converted from analog to digital, manipulated digitally, and then converted back to analog form. Figure 3 shows a typical digital

processing system. Note many digital signal processing applications have constraints on latency; that is, for the system to work, the digital signal processing operation must be completed within some fixed time, and deferred (or batch) processing is not viable." quoted from [17].

Figure 3-- Typical Digital Signal Processing System Diagram

Video signal processing algorithms are one type of digital signal processing algorithms. However, only high-performance DSPs are capable of meeting real-time requirements [8]. The challenge comes from the fact that the real-time video data throughput is very high as mentioned in section 1.1. The answers to this challenge are specific architectural enhancements addressing the data/computation throughput barrier in the new high-performance DSPs. The following discussed features are considered most useful for real-time video and image processing.

DSPs have been optimized for repetitive computation kernels with special hardware addressing modes like circular or modulo addressing mode. Such hardware addressing modes allows circular buffers to be implemented without having to constantly test for wrapping by software. Saving software operations is equal to saving time. This is especially beneficial for low level image/video processing operations such as convolution that contain intensive inner loops.

DSPs also have highly parallel architectures in a general sense. Most of DSPs have multiple functional units and VLIW/SIMD features. These features allow multiple

operations to be performed by a single long instruction and also multiple data are manipulated by a single instruction. These features can be used to exploit the inherit parallelism in image/video processing.

In addition, DSPs have been designed with high memory bandwidth in mind. On-chip DMA controllers, multilevel caches, and the buses connecting all the components together allow efficient data transferring between memories and devices. DMA controllers, particularly, access system memories independently and transfer data from and to the memories on the demand of processing units. With DMA taking care of the data transferring, processing units save time from less reading and writing operations. With more time that can be used in data processing, higher data throughput is allowed in the system. This is definitely very favored by real-time video processing because high data throughput is the challenge in the first place.

Besides the above three features, modern DSPs also have some other good features that are beneficial to general digital signal processing including the video signal processing. For example, DSPs often use memory architectures like Harvard architecture or a modified von Neumann architecture that are able to fetch multiple data and/or instructions at the same time. Another feature or trend perhaps, is that much higher frequency is allowed than before. New high-performance DSPs can work off frequency at the order of GHz, for example Davinci video processors [18] are able to work over 1 GHz. The features mentioned above make DSP a viable option for inclusion in a real-time video processing system.

### **DSP-based Implementations**

DSP-based platforms have been found to be particularly popular in image filtering implementations. The reason is most likely that the looping computation structure of image filtering fits the DSPs architecture very well. Among all sorts of image filtering problems, non-linear filtering is relatively more challenging. One research group has consistently shown a single-chip high-performance DSP's capability in real-time non-linear filtering [19, 20, 21, 22, 23]. In [20, 21, 22], it was shown that by using a DSP-based platform, a real-time video rate (25 fps) edge-preserving, non-linear filtering could be achieved for 176×144p, so called Quarter Common Image Format (QCIF). High-performance DSPs were used in these implementations: TMS320C6701 DSP running at 167 MHz was used in [20] and TMS320C6711 DSP running at 150 MHz was used in [21, 22].

For moving object detection, however, the DSP-based platform is not often used. And most implementations use optical flow algorithms over the background modeling ones. For example, Iketani, Kuno, and Shimada et al. [24] employed 9 TMS320C40 DSPs with each performing a single operation of the optical flow algorithm in a video surveillance system and the system was able to run with the video resolution of 1024×256p at 15 fps. It is only very recently, with the newly available high-performance DSPs, implementations using background modeling algorithms have emerged. Published in December, 2013, a team implemented their background modeling algorithm on TI's high-performance TMS320DM642 DSP and achieved the performance of 352×288@14 fps [25].

### 2.1.2. FPGA Platform Review

### **FPGA Architecture**

FPGA stands for Field-Programmable Gate Array. It is an integrated circuit designed to be configured or reconfigured into a custom circuit by the user after manufacturing hence "field-programmable". Its basic architecture is an array of logic blocks (that logically are equivalent to a combination of logic gates and flip-flops) and I/O pads with a network of programmable interconnects [26] hence "gate array".

Each logic block (called Configurable Logic Block (CLB) or Logic Array Block (LAB), depending on FPGA vendor) has the potential to be configured into many types of logic and can be connected to many other logic blocks and I/O pads via routing channels (networks) by programming the interconnects (switch box, whenever a vertical and horizontal channel intersect). Modern FPGA families can provide over 10 thousand logic blocks (e.g., Virtex6 FPGA family [27]). Considering the combination of these logic blocks, FPGAs today are capable of providing countless possibilities of implementations in terms of circuit logic and interfaces. In addition to the above capabilities, modern FPGAs also have included higher level functionalities, (e.g., multipliers, generic DSP blocks, embedded processors, high speed I/O logic, embedded memories, etc.) fixed into silicon. Having these common functions embedded into the silicon, reduced the area required and gave those functions increased speed compared to building them from primitives.

### **FPGA Programming**

To define the behavior of the FPGA, the hardware description language (HDL) or schematic design can be used.

In practice, design files (in HDL or schematic) that represent desired circuit logic are provided to EDA tools along with constraint files. EDA tools translate the high-level design files to a binary file that is ready to be downloaded onto a targeted FPGA device to configure it.

The above process appears to be similar to that of compiling source code, written in software programming language, into executable code in machine language. Nevertheless, there is a significant difference. FPGA programming aims to implement custom digital circuits on the FPGA. Software programming, on the other hand, aims to produce executable code that can run on a processor.

EDA tools for programming FPGAs vary from vendor to vendor. However, they follow a similar road map and translate users' design step by step. Usually there are 6 steps involved.

- Synthesis: This step translates the high-level circuit design to a netlist that describes

the circuit by listing its instances and their connectivity. An "instance" can be

anything from a simple register to a complex digital circuit.

- 2. Translation: This step "unfolds" the hierarchical instances in the previous netlist so only primitives are instanced in the new netlist. A "primitive" is an element that cannot be further unfolded such as a register or a logic gate.

- 3. Map: This step maps the primitives of the input netlist onto the physical resources (e.g., CLB, I/O pads, DSP blocks, etc.) in a targeted FPGA device and generates a new netlist that describes the circuit design physically, whereas the previous netlists do it logically.

- 4. Place and Route: This step defines how device resources are located and interconnected inside an FPGA. The definition is added to the previous physical netlist.

- 5. Programming File Generation: This step uses the physical netlist to generate a binary file for FPGA device configuration.

- 6. FPGA Configuration: This step downloads the binary file to the FPGA device to configure it.

### **FPGA Advantages**

A digital circuit implemented in an FPGA is customizable. This nature is beneficial to implement video processing algorithms in many ways.

First, one can design glue logic on FPGA to connect it to useful devices in video processing like a camera board, an off-chip memory, video display devices, etc.

Second, one can optimize a video processing circuit in the FPGA to give the best possible data throughput. For example, one can exploit different levels of parallelism inherent in an image/video processing algorithm by using multiple identical functional units (e.g., multiple arithmetic logic units or even multiple microprocessors) in parallel or putting all necessary functional blocks in a chain running in synchronization (e.g., pipelining) or a hybrid of the former two.

Third, one can use custom memory configurations and/or addressing techniques in an FPGA to exploit efficiency in data locality of video data. Note video data is three-dimensional data and memories are initially designed for one-dimensional data only.

In addition, one can accurately define data processing time in an FPGA-based design. Data in a digital circuit is transferred via registers. Registers are known for synchronizing circuit's operation at the edge of the clock signals. A register in the data path introduces one clock delay for transferring data. Delay is known to the designer in simple circuits or can be accurately estimated by EDA tools.

In summary, FPGA-based design can interface multiple devices easily and achieve high data throughput both in the inner circuit and memory bandwidth. Plus its data processing time is very predictable. These advantages are very useful for all kinds of video processing implementations.

### **FPGA-based Implementations**

FPGA-based platforms have been used to implement many video processing algorithms particularly in low-level image/video operations, e.g., image filtering operations, edge detection, moment calculation, Hough transform, image/video compression, etc.

In many cases, an FPGA platform has the potential to meet or exceed the performance of a single DSP or multiple DSPs. Since non-linear filtering examples have been presented in section 2.1.1, we also present FPGA-based non-linear filtering implementations here. An example of such an implementation was shown in [28] and the reported results showed that this implementation allowed an image of 512×512p to be filtered within 98 ms (≈11 fps) when the FPGA works off 8 MHz or within 23 ms (≈43 fps) when the FPGA works off 33.3 MHz. Another encouraging example is that of a fuzzy morphological filter implementation [29] which achieved a performance of 179 fps for 512×512p.

For moving object detection using background modeling algorithms, several FPGA-based examples also have been found. Two teams have consistently worked on the real-time solution of moving object detection. A team at Lund University, Sweden, presented a validated solution that is able to perform real-time moving object detection in video of 640×480p@25fps [30, 14, 31]. Another team at University of Napoli Federico II, Italy, presented their validated solution that is capable of real-time moving object detection in video of 1280×720p@20fps [32, 33, 34]. Kryjak, Komorkiewicz, and Gorgon in another separate work gave a performance of 640×480p@60fps [35].

### **2.1.3. Summary**

From the above review of DSP-based platforms and FPG-based platforms, the following two conclusions are drawn:

- For image filtering implementations, FPGA-based and DSP-based platforms seem to be equally used. However, in general, the FPGA-based platforms can outperform DSP-based ones significantly for this application.

- 2. In moving object detection implementations, FPGA-based platforms are preferred by researchers. The achieved real-time performance shows that FPGA-based platforms have the potential to outperform the DSP-based ones.

Based on the above conclusions, an FPGA-based platform was chosen to develop and implement the solution. Specifically, for this thesis, the Xilinx ML605 evaluation board (for details of ML605 please refer to [36]) was selected for its abundant available resources and potential capabilities of performing real-time video processing. The ML605 board has

a Virtex6-xc6vlx240t FPGA (for more information about this FPGA model please refer to [27]) on the board.

### 2.2. Review of Milestone Statistical Background Modeling Algorithms

Elhabian, El-Sayed, and Ahmed [37] classified the background modeling algorithms into two categories, recursive and non-recursive. The recursive method mainly contains two types of algorithms, recursive filters [38], and parametric statistical modeling [11, 12]. The non-recursive method mainly contains non-recursive filters [39, 40, 9, 41] and non-parametric statistical modelling techniques [13].

Cheung and Kamath [10] also surveyed background modeling algorithms based on a similar classification and also compared their performance. They remarked that statistical modeling algorithms generally outperform the filter ones.

A recent survey by Bouwmans [42] classified the background modeling algorithms into 5 categories. He remarked that the most frequently used models are the statistical in nature due to their robustness in changing environment, such as illumination change in a day.

Based on the previous systematic reviews in this field, the focus in this chapter is on three milestone statistical background modeling algorithms, namely single Gaussian modeling [11], a mixture of Gaussian modeling [12], and kernel density estimation [13].

### 2.2.1. Common Ground of Statistical Background Modeling Algorithms

Before describing details of each selected algorithm, it is helpful to have pre-knowledge of the common ground of the statistical background modeling algorithms that were investigated.

As mentioned in the Chapter 1, the result of background modeling algorithms is foreground and background segmentation at each frame of the video. But unlike other segmentation approaches that classify pixels of an image based on the information in the spatial domain, background modeling does it in the temporal domain at each individual spatial position. A pixel is defined as the intensity value of a position in the (x, y) plane at the frame number t. Then the set of all the pixels in a video is  $\{I_{(x,y,t)}|x,y,t\in N,1\leq x\leq H,1\leq y\leq W,t>1\}$  where I represents the intensity value, H is the height of the frame, W is the width. The members of  $I_{(x,y,t)}$  are independent to each other. At a given position  $(x_0,y_0)$ ,  $\{I_{(x_0,y_0,t)}|t\in N,t>1\}$  is a time series. A statistical background modelling algorithm estimates the statistical properties of every time series on-the-fly and generates the corresponding classification time series accordingly, e.g.  $\{fb_{(x_0,y_0,t)}|t\in N,t>1\}$ , where fb is either 1 i.e. foreground or 0 i.e. background. When every position in the (x,y) plane of the current frame is classified either as foreground or background, the entire frame is segmented i.e.  $\{fb_{(x,y,t)}|x,y\in N,1\leq x\leq H,1\leq y\leq W,t=t_0\}$ .

Most statistical background modeling algorithms have two sets of operations, namely model estimation, and foreground/background classification. Each algorithm investigated below is organized in this manner.

### 2.2.2. Single Gaussian Algorithm

Wren, Azarbayejani, and Darrell, et. al. [11] introduced a single Gaussian (SG) modelling algorithm in a gesture recognition system. However, the formalization of the algorithm is generalized in later work by Bouwmans et al. [43]. In the SG algorithm, the time series  $\{I_{(x,y,t)}|x,y,t\in N,1\leq x\leq H,1\leq y\leq W,t>1\}$  is modeled by a single

Gaussian. Then the probability of observing an intensity value at any position of a frame is defined as follow:

$$P(I_{(x,y,t)}) = \eta(I_{(x,y,t)}, \mu_{(x,y,t)}, \sigma_{(x,y,t)}^2)$$

Where  $\eta$  is the Gaussian probability density function,  $\mu_{(x,y,t)}$  is the estimation of the mean and  $\sigma^2_{(x,y,t)}$  is the estimation of the variance.

The estimation principle of the SG algorithm is:

$$\mu_{(x,y,t)} = a \cdot \mu_{(x,y,t-1)} + (1-a) \cdot I_{(x,y,t)}$$

$$\sigma_{(x,y,t)}^2 = a \cdot \sigma_{(x,y,t-1)}^2 + (1-a) \cdot \left(I_{(x,y,t)} - \mu_{(x,y,t)}\right)^2$$

where a is the forgetting rate, a number smaller than but very near to 1.

The classification principle is:

$$fb_{(x,y,t)} = \begin{cases} 0, background, if \left| I_{(x,y,t)} - \mu_{(x,y,t)} \right| \leq K \cdot \sqrt{\sigma_{(x,y,t)}^2} \\ 1, foreground, if \left| I_{(x,y,t)} - \mu_{(x,y,t)} \right| > K \cdot \sqrt{\sigma_{(x,y,t)}^2} \end{cases}$$

where *K* is used to adjust the sensitivity of the foreground detection. In essence it decides the credible interval of the observations being background.

As simple as SG is, it is considered as a milestone algorithm for the initial introduction of statistical tools into this field. The algorithm is characterized as being suitable to deal with a stable environment with moderate illumination change [42]. A sudden change of background objects, or in illumination, will cause miss-classification at the beginning, but will be adapted gradually thanks to its on-the-fly estimating nature.

### 2.2.3. Mixture of Gaussian Algorithm

The mixture of Gaussian modelling (MOG) algorithm was proposed by Friedman and Russell [44] for a traffic surveillance system. In their algorithm, each time series at a position uses a mixture of three Gaussians of which each corresponds to road, vehicle, or shadow. This version of MOG initializes the Gaussian models using an off-line Estimate Maximum (EM) algorithm. The Gaussian models are heuristically labeled by the rule: The Gaussian model with the darkest mean value is shadow, of the remaining two, the one with the larger variance is labeled as vehicle, and the other is labeled as road. From this point, the label of each Gaussian model remains fixed. For classification, each pixel is labeled according to its Gaussian model's label. The model maintenance is the incremental EM algorithm.

Stauffer and Crimson [12] generalized the above idea by using a mixture of k Gaussians. Compared to the MOG proposed by Friedman and Russell [44], this new version MOG has a greater flexibility in number of Gaussian and distribution's label of each is not fixed. The probability of observing the current intensity value is given by the weighted average of probabilities in k Gaussian models. This probability is given by the following formula (for simplicity, the index x and y are omitted in the formula):

$$P(I_t) = \sum_{i=1}^k \omega_{i,t} \cdot \eta(I_{i,t}, \mu_{i,t}, \sigma_{i,t}^2)$$

where k is the number of Gaussians,  $\omega_{i,t}$  is the weight of the  $i^{th}$  Gaussian model with the mean estimation  $\mu_{i,t}$  and variance estimation  $\sigma_{i,t}^2$ . Note these k Gaussian models are descending ordered following the criterion ratio of  $\omega_{i,t}/\sigma_{i,t}$  at time t.

The estimation principle has two cases and the case selected for each situation depends on if the "matching condition" is true for one of the models or none of them. The "matching condition" is:

$$\left|I_t - \mu_{i,t}\right| \le K \cdot \sqrt{\sigma_{i,t}^2}$$

where K is a constant to adjust the credible interval of the observations that are matched to a Gaussian model. The first case is that a match is found, i.e. the "matching condition" is true for one of the k Gaussians. Note if the "matching condition" is true for more than one Gaussian, only the first match is adopted. The second case is that no match is found.

If it is the first case, the estimation principle of models' weights is:

$$\omega_{i,t} = a \cdot \omega_{i,t-1} + (1-a) \cdot M_{i,t}$$

where a is forgetting rate and  $M_{i,t}$  is 1 for the Gaussian model which is matched and 0 for the rest of them. After this estimation, the weights are normalized to guarantee that the sum of all the weights is 1, i.e.  $\sum_{i=1}^{k} \omega_{i,t} = 1$ .

The  $\mu_{i,t}$  and  $\sigma_{i,t}^2$  parameters for unmatched Gaussian models remain the same, while the parameters of the model which matches the new observation are updated as follows:

$$\mu_{i,t} = \rho \cdot \mu_{i,t-1} + (1 - \rho) \cdot I_t$$

$$\sigma_{i,t}^2 = \rho \cdot \sigma_{i,t}^2 + (1 - \rho) \cdot (I_t - \mu_{i,t})^2$$

where:

$$1 - \rho = (1 - a) \cdot \eta(I_{i,t}, \mu_{i,t-1}, \sigma_{i,t-1}^2)$$

If it is the second case, the least Gaussian model, the  $k^{th}$  model is replaced with a new one with:

$$\begin{cases} \omega_{k,t} = Low \ Priority \ Weight \\ \mu_{k,t} = I_t \\ \sigma_{k,t}^2 = Large \ Initial \ Variance \end{cases}$$

As to the classification principle, whether the latest observation is foreground or background depends on which Gaussian model the latest observation falls into. The first *B* Gaussian models are defined as "background Gaussian models". *B* is calculated as follow:

$$B = \underset{b}{\operatorname{argmin}} \sum_{i=1}^{b} \omega_{i,t} > Th$$

where Th is a proper threshold that divides the first B and rest of the Gaussian models. This division is based on the sum of the first b models' weights,  $\sum_{i=1}^{b} \omega_{i,t}$ .

The classification time series is generated as follow:

$$fb_t = \begin{cases} 0, background, if \ the \ I_t \ matches \ one \ of \ the \ first \ B \ models \\ 1, foreground, if \ the \ I_t \ matches \ none \ of \ the \ first \ B \ models \end{cases}$$

The MOG algorithm is considered as a milestone because it introduced parametric multi-models into this field. Compared to the SG algorithm, the MOG is more adaptive for outdoor scenes since some periodical background change can fit in more than one Gaussian model and still be classified as background.

### 2.2.4. Kernel Density Estimation (KDE)

Elgammal, Harwood, and Davis [13] proposed an algorithm estimating the probability density function using the kernel estimator for N intensity samples  $\{x_1, x_2, ..., x_N\}$ . The probability of observing the latest pixel intensity value  $I_t$  is considered given by the following formula:

$$P(I_t) = \frac{1}{N} \sum_{i=1}^{N} K(I_t - x_i)$$

where  $K(\cdot)$  is the kernel. These samples are initialized with N observations from a time window of W. The window contains the W latest pixel intensity observations,  $\{I_{t-W+1}, I_{t-W+2}, ..., I_t\}$ . Either N = W or the N samples are N/2 pairs of consecutive observations in the time window. Elgammal et al. suggested that kernel  $K(\cdot)$  should be a normal destribution function  $\mathcal{N}(0, \sigma^2)$  and the initial two sets of samples should be initialized. One set is for the "short term" estimation, the other is for the "long term" estimation.

The estimation principle in essence is altering the oldest pair of elements in the samples with the latest pair of consecutive observations. As mentioned above, there are two types of estimation:

- Short term estimation uses a smaller time window to initialize a smaller set of samples. The altering is performed with a selective mechanism so that only if the latest observation is classified as background, the consecutive pair it belongs to will be adopted into the samples.

- Long term estimation uses a larger time window to initialize a larger set of samples.

And the samples are altered blindly.

The classification principle is:

$$fb = \begin{cases} 0, background, if \ P_{long}(I_t) < Th \ and \ P_{short}(I_t) < Th \\ 1, foreground, if \ P_{long}(I_t) \ge Th \ or \ P_{short}(I_t) \ge Th \end{cases}$$

where Th is a manually set global threshold.  $P_{long}(I_t)$  is the probability of observing  $I_t$  calculated with the long term samples,  $P_{short}(I_t)$  is that with the short term samples.

In addition to the new technique for background modeling, a false detection reduction strategy and a shadow reduction strategy are also introduced by Elgammal et al. The former is based on local neighborhood pixels and the latter is based on color scaling.

KDE initially introduced non-parametric modeling into background modeling. Elgammal et al. claimed that this algorithm is more sensitive in detecting a moving target than the parametric ones and less affected by the presence of the target in the scene. Bouwmans [42] also commented that KDE is more adapted for outdoor scenes where dynamic backgrounds appear but less suited for illumination changes.

# **III.** Solution Development

This chapter describes the road map of developing the real-time MOD solution. The ML605 FPGA-based platform was selected for the proposed solution based on the discussion in section 2.1. Based on the review in section 2.2 and memory considerations, this chapter discusses the algorithm selection and its enhancement. The features of the system are then discussed and the overall design is introduced in the end of this chapter.

### 3.1. Algorithm Selection and Improvement

In section 2.1.3, an FPGA-based platform was selected for the real-time MOD solution. There are different concerns for implementing a background modeling algorithm on an FPGA than on the conventional PC-based platform. The primary concern is memory related. In this section, the memory related considerations will be discussed first, then specific considerations for each of the three algorithms. The SG algorithm is selected and is discussed further. In the end, the SG algorithm is enhanced before being mapped into the design of the solution.

# **3.1.1.** Memory Related Considerations

# **Memory Storage Requirements Consideration**

Three statistical background modeling algorithms and their common ground were introduced in section 2.2.1. In background estimation, current pixel intensities with either the digital value of the latest statistical parameters or historical pixel intensities are used. This indicates that memory storage is required for keeping these data during the background estimation. Given that multiple parameters are required for each pixel's

background estimation and the number of pixels of each frame is on the order of a million for HD videos, the required memory amount could easily exceed that available by the on-chip memory (e.g., Virtex6-xc6vlx240t FPGA has a maximum of 15 Mb [27]). An off-chip DDR3 SDRAM was used to meet the memory storage requirement since it is the fastest and largest memory available on the ML605 board.

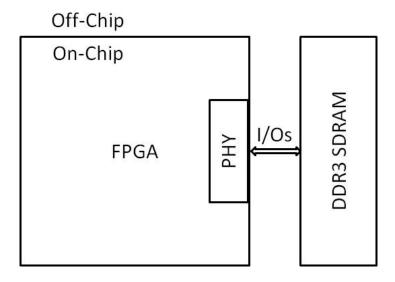

### **Memory Bandwidth Consumption Consideration**

SDRAM, like many other generic memory systems, was originally designed for one-dimensional data access and thus cannot properly address the spatial locality necessary for two-dimensional or three-dimensional image and video data [8]. Figure 4 shows that there is only one port that interfaces the FPGA chip with SDRAM at the physical layer (PHY).

Figure 4-- Memory Interface at PHY

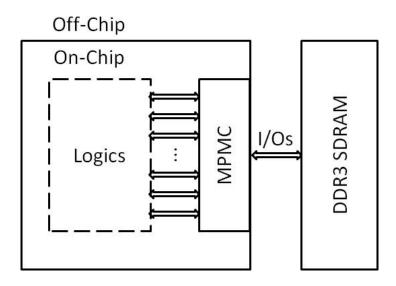

Custom memory addressing schemes were needed to allow efficient memory access of multi-dimensional data. Moreover, arithmetic operations prefer simultaneous access to all needed data. To get multiple pieces of data from memory, and to write multiple parameters

back to memory, a multi-port memory interface is needed. Given that designing a memory controller from primitives is a non-trivial work, a customizable multi-port memory controller (MPMC) IP core [45] was used in the design to meet the memory interface preference. An IP (intellectual property) core is a block of logic or data that is used in FPGA-based circuit design. It can be designed by the user, provided by FPGA vendor, or provided by third party. Figure 5 shows a simplified diagram of a multi-port memory controller that interfaces other FPGA Logics with off-chip memory.

Figure 5 -- MPMC Interface Diagram

The MPMC can provide several video frame buffer connectors (VFBC, for more information please refer to [45]) that can access two-dimensional data separately and efficiently. Such a property is favored in video processing; however, certain limitations are attached. There are a limited number of ports available to be configured as VFBC and each VFBC port has a fixed size data bus (number of bits for transferring data). In other words, there are a limited number of bits available to represent background model parameters for each pixel. This number is 32 for the MPMC IP core.

### 3.1.2. Algorithms Analysis and Comparison

Given that only 32 bits are available, the number of parameters to be represented becomes the issue since more parameters means more loss of precision in calculations. This is extremely important for background estimation for each pixel which is an on-line iterative process and losing precision excessively may neutralize the effect of this process. In this context, we prefer a fewer number of background modelling parameters with greater precision. Table 2 lists the name and number of parameters for each algorithm discussed in section 2.2.

Table 2 -- Parameters and Their Average Bits on Data Bus

| Algorithm | Parameters              | Number   | Number of bits for each parameter (average) |  |

|-----------|-------------------------|----------|---------------------------------------------|--|

| SG        | Mean                    | 2        | 16                                          |  |

|           | Variance                | 2        |                                             |  |

| MOG       | Mean×3                  |          |                                             |  |

|           | Variance×3              |          |                                             |  |

|           | Weight⅓                 | 12       | 2-3                                         |  |

|           | Order×3                 |          |                                             |  |

|           | (For 3 Gaussian Models) |          |                                             |  |

| KDE       | Samples                 | 32 (max) | 1                                           |  |

Observed from Table 2, the SG algorithm has the smallest number of parameters with the greatest precision per parameter so the SG algorithm was selected for further discussion in section 3.1.3.

### **3.1.3.** SG Algorithm Enhancement

In this section, an enhanced version of the selected SG algorithm is proposed. Firstly, the SG algorithm is evaluated after optimization. Then the enhanced SG algorithm is

proposed based on the analysis of the evaluation. Finally, the enhanced SG algorithm is also evaluated by comparing its results with the optimized SG algorithm's results.

#### **SG** Evaluation

The SG algorithm was evaluated by optimizing the constants a and K then continuing with observing the segmentation results using the optimized constants. For optimization, a measurement of the similarity between the segmentation result and "ground truth" is used, namely the Jaccard Similarity coefficient (JC coefficient, please see section below). The bigger the JC coefficient is the more similar the segmentation result to the "ground truth". The optimum pair of a and K gives the maximum JC coefficient for a given frame. The wallflower data set [9] provides several sets of image sequences and each set has one image with a hand segmented "ground truth". More details of "ground truth" provided in wallflower data set are discussed below.

### **Step1: SG Constants Optimization**

### *IC* coefficient:

The JC coefficient is named after Paul Jaccard (18 November 1868 in Sainte-Croix - 9 May 1944 in Zurich) who was a professor of botany and plant physiology at the ETH Zurich. The coefficient was initially included in a biology book [46]. Rosin and Ioannidis [47] referred to [46] and interpreted the JC coefficient as a measurement in pixel-based evaluation of image thresholding for change detection, where the coefficient is calculated with three values, namely true positive (TP), false positive (FP), and false negative (FN). The JC coefficient formula was given as follows:

$$JC = \frac{TP}{TP + FP + FN}$$

Elhabian et. al. [37] referred to [47] and regarded this measurement as a pixel-based method for quantifying the performance of image segmentation in moving object detection.

In moving object detection, the specifications of the TP, the FP, and the TN are:

- *TP*: the number of foreground pixels correctly detected; It is equivalent to the number of pixels that are foreground both in the segmentation result and in "ground truth".

- *FP*: the number of background pixels incorrectly detected as foreground (also known as false alarms); It is equivalent to the number of pixels that are foreground in the segmentation result but background in "ground truth".

- *FN*: the number of background pixels incorrectly detected; It is equivalent to the number of pixels that are background in the segmentation result but foreground in "ground truth".

## Wallflower data set:

As mentioned above, the wallflower data set provides several sets of image sequences and each set has an image with a hand segmented ground truth. Three sets of image sequences were selected, namely 'Time of Day', 'Bootstrap', and 'Waving Trees'. 'Time of Day' has 5890 images and the 1850<sup>th</sup> image is provided with a ground truth of foreground/background segmentation. 'Bootstrap' has 3055 images and the 300<sup>th</sup> image is provided with a ground truth. 'Waving Trees' has 287 images and the 248<sup>th</sup> is provided with a ground truth. The images with the provided 'ground truth' are referred to as 'targeted

frames' in the following sections since only these frames' segmentation results have reference to compare with and were used in evaluating the algorithm. Figure 6 shows these special images with their provided 'ground truth'.

Figure 6 – Targeted Frames and Their Ground Truth

### Optimization Principle:

For each pair of a and K there is a segmentation result of the targeted frame in each data set. So the JC coefficient can be calculated accordingly. The optimization principle is simply to find the maximum JC coefficient in a-K plane and retrieve the pair of a and K as the optimized constants of the SG algorithm for the data set the targeted frame belongs to.

# Optimization Result:

Figure 7 shows the relationship between the a-K plane and the JC coefficient of the targeted frame (i.e.  $1850^{th}$  frame) in data set 'Time of Day'. Figure 7 shows that the maximum JC coefficient is 0.61649, and the correspondent pair of [a, K] is [0.993, 2.3].

Figure 7 -- K-a-JC Surface of 'Time of Day' Data Set

Similarly, for the 'Bootstrap' data set, the maximum JC coefficient is 0.28235, correspondent [a, K] is [0.99, 0.6] (Figure 8); for 'Waving Trees' data set, the JC coefficient is 0.61317, correspondent [a, K] is [0.994, 1.8] (Figure 9). The optimized constants [a, K] and maximum JC coefficients of each target frame in every data set are listed in Table 3.

### Bootstrap

Figure 8 -- K-a-JC Surface of 'Bootstrap' Data Set

### Waving Trees

Figure 9 -- K-a-JC Surface of 'Waving Trees' Data Set

Table 3 -- Optimized SG Constants and Maximum JC Coefficients of Each Data Set

| Data set                           | SG algorithm Constants | JC coefficients of the target frame |  |

|------------------------------------|------------------------|-------------------------------------|--|

| Time of Day                        | a = 0.993<br>K = 2.3   | 0.61649                             |  |

| Bootstrap                          | a = 0.99 $K = 0.6$     | 0.28235                             |  |

| Waving Trees $a = 0.994$ $K = 1.8$ |                        | 0.61317                             |  |

**Step2: Observing the Optimized Segmentation Results**

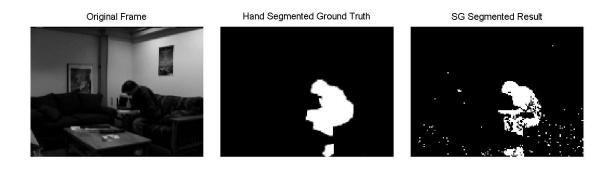

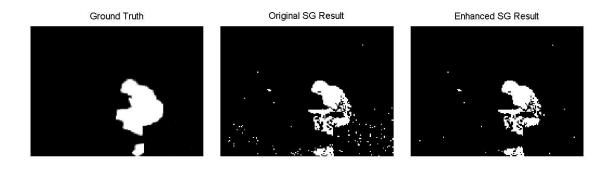

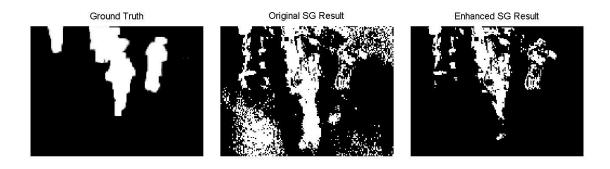

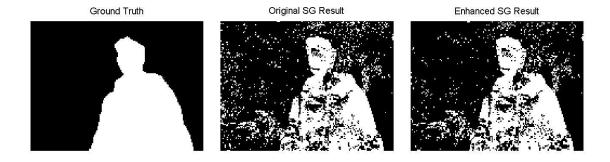

Figure 10, Figure 11, and Figure 12 show the targeted frames, their ground truth, and its optimized segmentation result by the SG algorithm.

Figure 10 -- Targeted Frame, Ground Truth, and SG Segmented Result in 'Time of Day'

Figure 11 -- Targeted Frame, Ground Truth, and SG Segmented Result in 'Bootstrap'

Figure 12 -- Targeted Frame, Ground Truth, and SG Segmented Result in 'Waving Trees'

By observing the segmentation results, the most significant defect in the results is false positive (FP). Since they appear as white dots in the segmentation results, it is referred to as 'salt' noise as well.

## **Noise Analysis and Reducing**

# **Step1: Noise Analysis**

'Salt' noise, as motioned above, is false positive in nature. To analyze the cause of this sort of positives, the SG algorithm process was observed at several individual positions in the (x, y) plane of the 'Time of Day' data set.

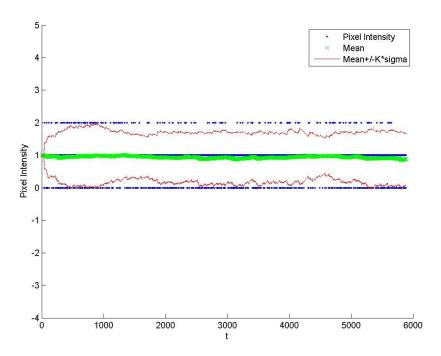

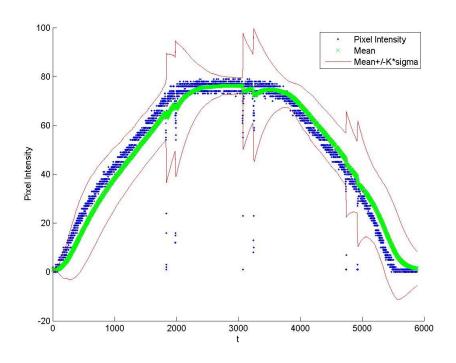

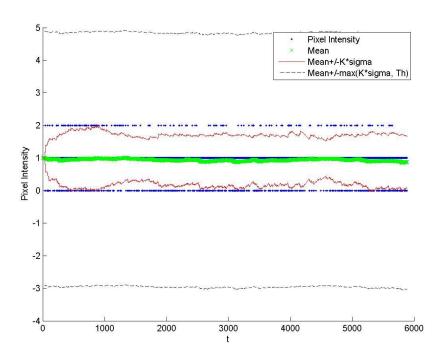

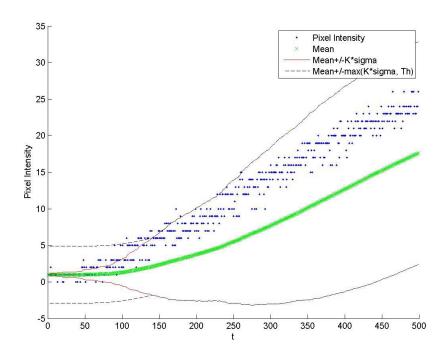

Figure 13 shows the sequences of pixel intensity  $(I_{(x,y,t)})$ , mean value  $(\mu_{(x,y,t)})$ , and classification boundaries  $(\mu_{(x,y,t)} \pm K \cdot \sqrt{\sigma_{(x,y,t)}^2})$  at position(x = 118, y = 147).

Figure 13 -- Pixel Intensity, Mean, and Classification Boundaries at [118, 147]

As observed from Figure 13, pixel intensity  $(I_{(x,y,t)})$  vibrates strictly between 0 and 2. This fact suggests that pixels at this position are actually all background for every frame. Yet many pixel intensities are observed beyond the boundaries  $(\mu_{(x,y,t)} \pm K \cdot \sqrt{\sigma_{(x,y,t)}^2})$  and are classified as positives. So the positives are all false positives. The total number of false positives is 704.

The reason why so many FP are observed here is because the classification boundaries  $(\mu_{(x,y,t)} \pm K \cdot \sqrt{\sigma_{(x,y,t)}^2})$  are too near to the mean values  $(\mu_{(x,y,t)})$ . And this is mainly due to the low amplitude of the intensity vibration (i.e.  $\pm 1$ ). As a consequence, in the SG algorithm, the variance  $(\sigma_{(x,y,t)}^2)$  (or standard derivation  $(\sqrt{\sigma_{(x,y,t)}^2})$ ) is too small to widen the boundaries to include the vibration itself.

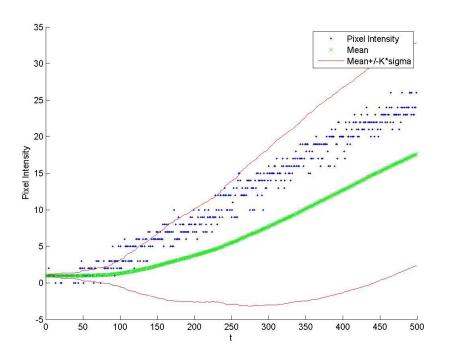

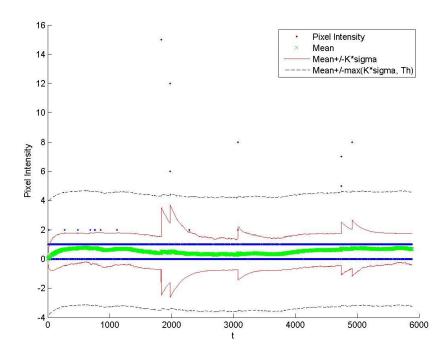

Figure 14 shows the sequences of pixel intensity  $(I_{(x,y,t)})$ , mean value  $(\mu_{(x,y,t)})$ , and classification boundaries  $(\mu_{(x,y,t)} \pm K \cdot \sqrt{\sigma_{(x,y,t)}^2})$  at position(x = 98, y = 14).

Figure 14 -- Pixel Intensity, Mean, and Classification Boundaries at [98, 14]

At this position, classification boundaries successfully distinguished some foreground pixels that are far from the mean values. But they also classified some pixels near to the mean values (i.e., with distance smaller than 2) as foreground. Such classifications are very likely to be false positives. The total number of positives is 37.

The misclassification issue here is mainly because of the rareness of some background intensities. Note that the nature of the SG algorithm is to classify the rare event as foreground by assuming the moving object appears rarely against the background. But this assumption cannot exclude the situation like 'rare background intensities'.

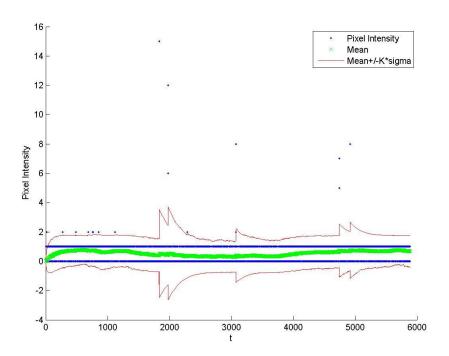

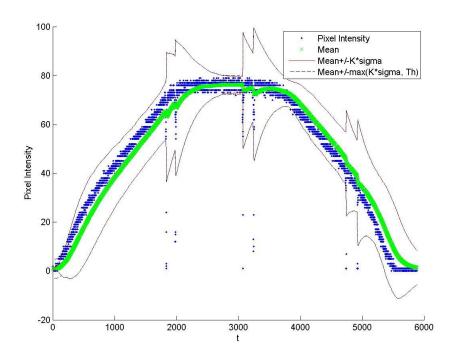

Figure 15 shows the sequences of pixel intensity  $(I_{(x,y,t)})$ , mean value  $(\mu_{(x,y,t)})$ , and classification boundaries  $(\mu_{(x,y,t)} \pm K \cdot \sqrt{\sigma_{(x,y,t)}^2})$  at position(x = 35, y = 1).

Figure 15 -- Pixel Intensity, Mean, and Classification Boundaries at [35, 1]

Figure 16 – Details of Start-up Period of Figure 15

At this position, the boundaries most ideally included the background pixels that are near the mean values and excluded foreground pixels that are far from them. However there are still some misclassifications at the beginning of the sequences (see Figure 16). This is because the SG algorithm needs some time to adapt the intensity variance. There are 110 positives in total.

From the above analysis, three causes of false positives were concluded:

- 1. Small variance  $(\sigma^2_{(x,y,t)})$  due to small vibration of the background intensities.

- 2. Rareness of some background intensities.

- 3. Start-up time to adapt the vibration of the pixel intensities.

All these three cause a narrow width between the classification boundaries ( $\mu_{(x,y,t)} \pm$

$K \cdot \sqrt{\sigma_{(x,y,t)}^2}$ ) making it a more difficult classification problem.

# **Step2: Noise Reduction**

To address the issue mentioned above and reduce the salt noise in segmentation, the following enhanced SG algorithm that can widen the coverage between boundaries is proposed:

The estimation principle is unchanged:

$$\mu_{(x,y,t)} = a \cdot \mu_{(x,y,t-1)} + (1-a) \cdot I_{(x,y,t)}$$

$$\sigma_{(x,y,t)}^2 = a \cdot \sigma_{(x,y,t-1)}^2 + (1-a) \cdot \left(I_{(x,y,t)} - \mu_{(x,y,t)}\right)^2$$

where  $\alpha$  is the forgetting rate, a number smaller than but very near to 1.

The classification principle is changed:

$$fb_{(x,y,t)} = \begin{cases} 0, background, if \left| I_{(x,y,t)} - \mu_{(x,y,t)} \right| \leq max(Th, K \cdot \sqrt{\sigma_{(x,y,t)}^2}) \\ 1, foreground, if \left| I_{(x,y,t)} - \mu_{(x,y,t)} \right| > max(Th, K \cdot \sqrt{\sigma_{(x,y,t)}^2}) \end{cases}$$

where K and Th are used to adjust the sensitivity of the foreground detection. Th makes sure that the width between the boundaries is no less than  $2 \cdot Th$  around the mean value  $(\mu_{(x,y,t)})$ .

#### **Enhanced SG Evaluation**

Similar to the evaluation of SG (SG **Evaluation** in section 3.1.3), the constants of the enhanced SG algorithm were optimized, and then the optimized segmentation results were observed. The optimized segmentation results of the enhanced SG algorithm were also compared to that of the original optimized SG algorithm.

## **Step1: Optimization**

Here the optimized a and K inherited from previous Step1: SG Constants Optimization were used. So only the Th needs to be optimized in this section. The optimization principle is finding the maximum JC coefficient by varying Th then retrieving the correspondent Th which is the optimum one.

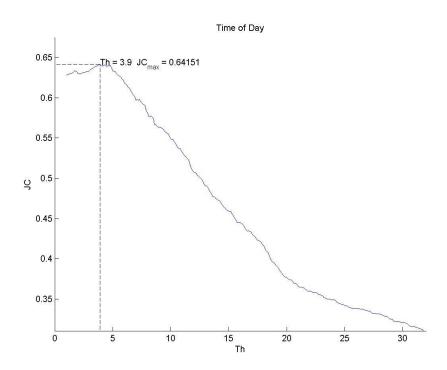

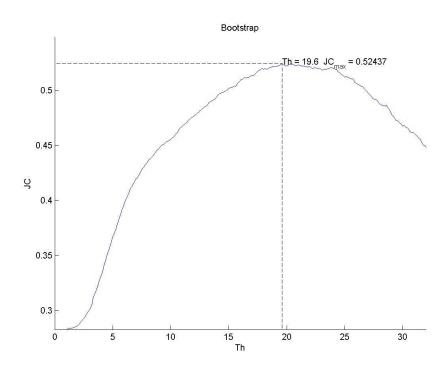

Figure 17 shows the Th - JC relationship of the targeted frame in the 'Time of Day' data set. Also the maximum JC coefficient and the optimum Th are marked in it. The similar content in 'Bootstrap' is shown in Figure 18 and that in 'Waving Trees' is shown in Figure 19.

Figure 17 -- Th-JC curve of 'Time of Day' Data Set

Figure 18 -- Th-JC curve of 'Bootstrap' Data Set

Figure 19 -- Th-JC curve of 'Waving Trees' Data Set

The optimization results were generalized in Table 4.

Table 4 -- Optimized Enhanced SG Constants and Maximum JC Coefficients

| Data set        | Enhanced SG algorithm constants | JC coefficient of the target frame |  |

|-----------------|---------------------------------|------------------------------------|--|

| Time of Day     | a = 0.993 $K = 2.3$ $Th = 3.9$  | 0.64151                            |  |

| Bootstrap       | a = 0.99 $K = 0.6$ $Th = 19.6$  | 0.52437                            |  |

| Waving<br>Trees | a = 0.994 $K = 1.8$ $Th = 11.6$ | 0.6362                             |  |

**Step2: Observation and Comparison**

Table 5 combines Table 3 and Table 4 and lists the improvement of *JC* coefficients introduced by the proposed enhancement on the SG algorithm.

Table 5 -- Comparison of Parameter Optimization between SG and Enhanced SG

| Data set        | SG<br>Constants      | JC by<br>SG | Enhanced SG<br>Constants         | JC by<br>Enhanced SG | JC<br>Improvement |

|-----------------|----------------------|-------------|----------------------------------|----------------------|-------------------|

| Time of<br>Day  | a = 0.993 $K = 2.3$  | 0.61649     | a = 0.993<br>K = 2.3<br>Th = 3.9 | 0.64151              | 0.02502           |

| Bootstraps      | a = 0.99 $K = 0.6$   | 0.28235     | a = 0.99<br>K = 0.6<br>Th = 19.6 | 0.52437              | 0.24202           |

| Waving<br>Trees | a = 0.994<br>K = 1.8 | 0.61317     | a = 0.994 $K = 1.8$ $Th = 11.6$  | 0.6362               | 0.02303           |

Figure 20 shows the sequences of pixel intensity  $(I_{(x,y,t)})$ , mean value  $(\mu_{(x,y,t)})$ , original classification boundaries  $(\mu_{(x,y,t)} \pm K \cdot \sqrt{\sigma_{(x,y,t)}^2})$ , and enhanced classification boundaries  $(\mu_{(x,y,t)} \pm max(Th,K \cdot \sqrt{\sigma_{(x,y,t)}^2}))$ . With the new enhanced boundaries, all the pixels were classified correctly as background. The number of false positives decreases from 704 (in Figure 13) to 0. In Figure 21, the new boundaries suppressed the rare background pixels that were false positives. The total number of positives decreases from 37 (in Figure 14) to 7. In Figure 22 and Figure 23, the enhanced classification boundaries reduced misclassification in the initialization stage of the algorithm. The total number of positives decreases from 110 (in Figure 15) to 65.

Figure 20 -- Pixel Intensity, Mean, and Enhanced Classification Boundaries at [118, 147]

Figure 21 -- Pixel Intensity, Mean, and Enhanced Classification Boundaries at [98, 14]

Figure 22 -- Pixel Intensity, Mean, and Enhanced Classification Boundaries at [35, 1]

Figure 23 – Details of Start-up Period of Figure 22

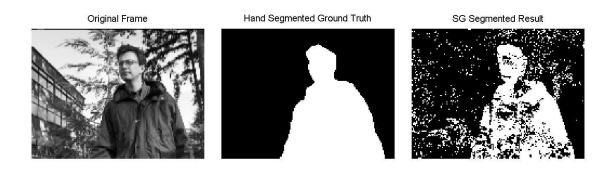

Figure 24, Figure 25, and Figure 26 show the ground truth, the optimized SG segmentation, and the optimized enhanced SG segmentation of the targeted frame of each data set. The segmentation results from our proposed algorithm have better quality than that from the original SG algorithm in terms of less false positives.

Figure 24 -- Truth Ground, Original, and Enhanced Segmentation of 'Time of Day' Data set

Figure 25 -- Truth Ground, Original, and Enhanced Segmentation of 'Bootstrap' Data set

Figure 26 -- Truth Ground, Original, and Enhanced Segmentation of 'Waving Trees' Data set

In summary, the proposed Enhanced SG algorithm efficiently reduces the number of false positives and increases the *JC* coefficient. More importantly, better quality of the segmentation results is perceived. So this enhanced SG algorithm was chosen to implement in the FPGA-base Real-Time MOD Design.

#### 3.2.Pre-knowledge and System Features

### 3.2.1. Pre-mentioned Facts

In previous sections of this chapter, three solution related facts that are mentioned:

- 1. FPGA based platform is used for designing.

- 2. Enhanced SG background modelling algorithm is to be mapped in the design.

- 3. Off-Chip memory and multi-port memory controller are necessary in the design.

The decision of using the FPGA based platform was made in section 2.1.3. The second decision of using enhanced SG algorithm was made in section 3.1.3. In discussion of memory related issues in section 3.1.1, the necessity of off-chip memory and multi-port memory controller was concluded. Figure 4 and Figure 5 in section 3.1.1 show diagrams of off-chip memory and multi-port memory controller.

### 3.2.2. Transferring Video Data in Real-Time

This project is about real-time video processing, so the system is to interface with a real-time video source and to transfer real-time segmentation results. It becomes important to understand transferring video data in real-time.

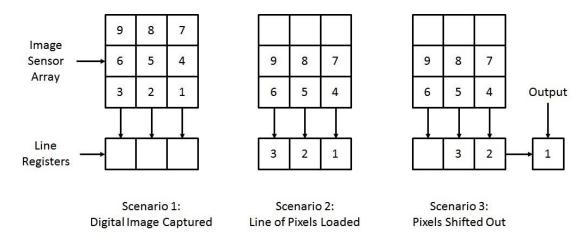

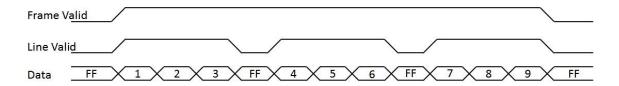

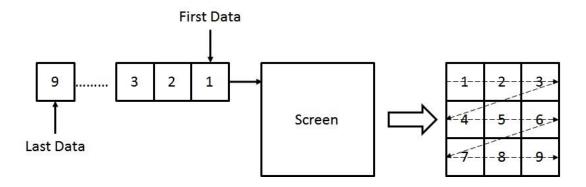

Modern cameras tend to have high resolution so each frame usually has the number of pixels in the order of millions. Since it is impractical to transfer millions of data at once, the common strategy is to transfer the data in the manner of one pixel after another in the group of lines. Figure 27 shows the signal transmitting principle of image sensors (e.g., CCD or CMOS). Figure 28 shows a virtual timing example of transferring video data.

Figure 27 -- Transferring Data of a Frame (3-by-3)

Figure 28 -- Virtual Timing Diagram of Transferring Video Data